# MediaPad 10 FHD Maintenance Manual

V1.0

For internal use only

| Prepared by | Yang Yongxiang | Date | 2012-7-14 |

|-------------|----------------|------|-----------|

| Reviewed by | Zhang Dewen    | Date |           |

| Approved by | Zhen Haitao    | Date |           |

All right reserved

# **Change History**

| Date      | <b>Revision Version</b> | Change Reason | Changed Chapter | Change Description | Author |

|-----------|-------------------------|---------------|-----------------|--------------------|--------|

| 2012-7-14 | V1.0                    |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

|           |                         |               |                 |                    |        |

# Contents

| 1 Product Overview                                                |    |

|-------------------------------------------------------------------|----|

| 1.1 Brief Introduction                                            | 8  |

| 1.2 Hardware Specifications                                       | 11 |

| 1.3 Software Specifications                                       | 12 |

| 1.4 Exploded View of the Host                                     | 12 |

| 2 Functional Chips                                                | 14 |

| 2.1 Hi3620                                                        | 14 |

| 2.1.1 Chip Specifications                                         | 14 |

| 2.1.2 Pin Assignment                                              | 15 |

| 2.1.3 Working Principles and Functions of the Hi3620              | 15 |

| 2.2 POP LPDDR2                                                    | 17 |

| 2.3 PMU Hi6421                                                    | 20 |

| 2.4 Wi-Fi and Bluetooth Modules                                   | 25 |

| 2.5 GPS BCM47511                                                  |    |

| 3 Layout of Major Components                                      | 32 |

| 3.1 Layout of Components on the S10 PCBA                          | 32 |

| 3.2 Components on the S10 PCBA                                    | 32 |

| 4 Principles and Failure Analysis                                 | 37 |

| 4.1 Working Principles of the MediaPad 10 FHD                     | 37 |

| 4.2 Power-On and Power Tree                                       |    |

| 4.2.1 Hardware Startup Process                                    |    |

| 4.2.2 Power Tree                                                  | 41 |

| 4.3 Circuit Analysis and Troubleshooting for Functional Units     | 42 |

| 4.3.1 Working Principles of the AP Subsystem                      | 42 |

| 4.3.2 Detailed Analysis of Working Principles of the AP Subsystem | 45 |

| 4.4 Circuit Analysis and Troubleshooting for the Modem Unit       | 65 |

| 5 Software Upgrade                                                | 73 |

| 5.1 Upgrade Preparation                                           |    |

| 5.2 Upgrading the Software by Using a USB Peripheral              | 73 |

| 5.2.1 Upgrading the Software by Using a microSD Card              | 73 |

| 6 Disassembly Procedure                                           | 75 |

| 6.1 Tools                     |    |

|-------------------------------|----|

| 6.2 Disassembly Preparation   | 75 |

| 6.3 Disassembly Procedure     | 75 |

| 6.4 Other Precautions         |    |

|                               |    |

| 7 Appendix                    |    |

| 7 Appendix<br>7.1 PCBA Layout |    |

|                               | 77 |

# Figures

| Figure 1-1 Appearance of the MediaPad 10 FHD                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 Hardware principles of the MediaPad 10 FHD                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 1-3 Exploded view of the host                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 2-1 Functional blocks of the Hi362014                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 2-2 Functional blocks of the POP LPDDR2 chip                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 2-3 Model of the POP LPDDR2 chip provided by ELPIDA                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2-4 Model of the POP LPDDR2 chip provided by Samsung                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 2-5 Pinouts of the POP LPDDR2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                     |

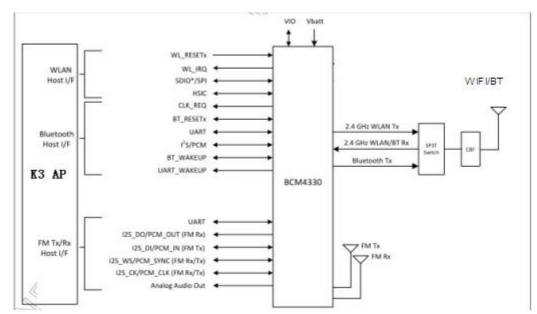

| Figure 2-6 Functional blocks of the power supply                                                                                                                                                                                                                                                                                                                                                                                                                              |

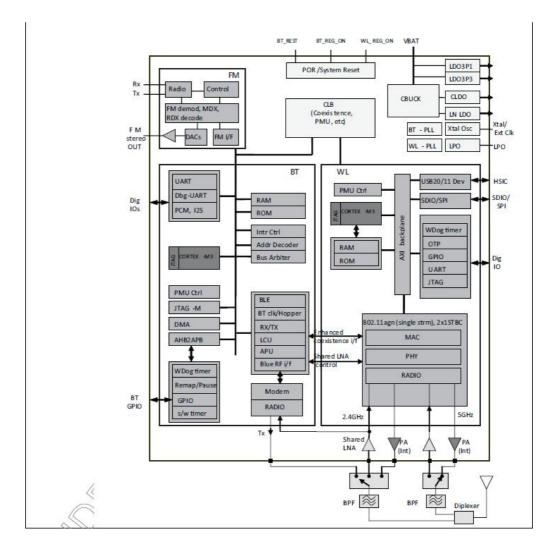

| Figure 2-7 RF solution for the Wi-Fi and Bluetooth modules of the S10                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2-8 Components encapsulated in the WI-FI or Bluetooth module                                                                                                                                                                                                                                                                                                                                                                                                           |

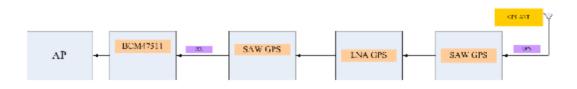

| Figure 2-9 RF solution for the GPS module of the S10                                                                                                                                                                                                                                                                                                                                                                                                                          |

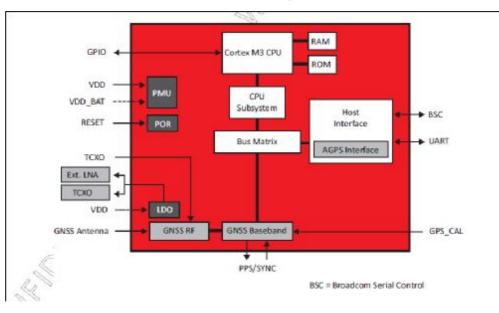

| Figure 2-10 Functional blocks of the BCM47511 chip                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

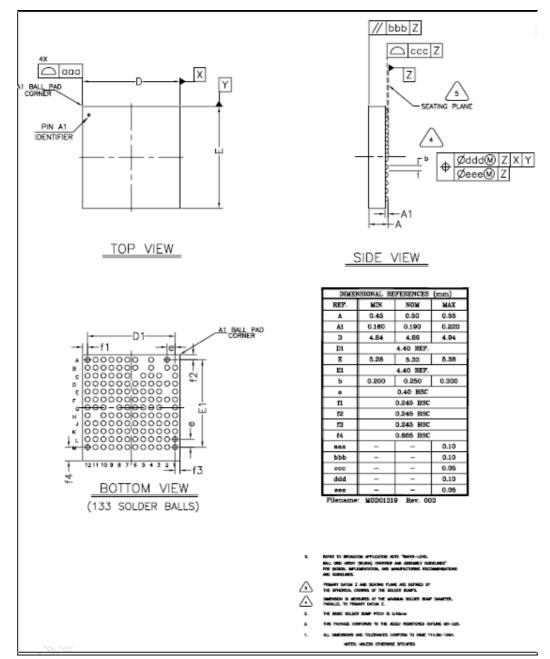

| Figure 2-11 Models of the BCM47511                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2-11 Models of the BCM47511                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 2-12 Components encapsulated in the BCM47511 chip                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 2-12 Components encapsulated in the BCM47511 chip                                                                                                                                                                                                                                                                                                                                                                                                                      |

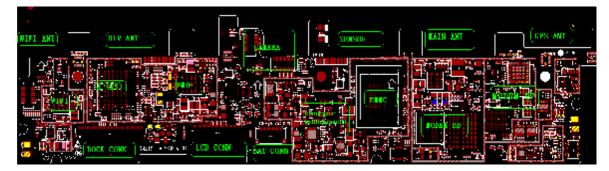

| Figure 2-12 Components encapsulated in the BCM47511 chip       31         Figure 3-1 Layout of components on the S10 PCBA       32         Figure 4-1 Functional blocks of the PCBA       38                                                                                                                                                                                                                                                                                  |

| Figure 2-12 Components encapsulated in the BCM47511 chip       31         Figure 3-1 Layout of components on the S10 PCBA       32         Figure 4-1 Functional blocks of the PCBA       38         Figure 4-2 Layout of components on the PCBA       38                                                                                                                                                                                                                     |

| Figure 2-12 Components encapsulated in the BCM47511 chip       31         Figure 3-1 Layout of components on the S10 PCBA       32         Figure 4-1 Functional blocks of the PCBA       38         Figure 4-2 Layout of components on the PCBA       38         Figure 4-3 Physical architecture of the PCBA       39                                                                                                                                                       |

| Figure 2-12 Components encapsulated in the BCM47511 chip       31         Figure 3-1 Layout of components on the S10 PCBA       32         Figure 4-1 Functional blocks of the PCBA       38         Figure 4-2 Layout of components on the PCBA       38         Figure 4-3 Physical architecture of the PCBA       39         Figure 4-4 Power-on and power-off sequencing       40                                                                                         |

| Figure 2-12 Components encapsulated in the BCM47511 chip       31         Figure 3-1 Layout of components on the S10 PCBA       32         Figure 4-1 Functional blocks of the PCBA       38         Figure 4-2 Layout of components on the PCBA       38         Figure 4-3 Physical architecture of the PCBA       39         Figure 4-4 Power-on and power-off sequencing       40         Figure 4-5 Power-on procedure       41                                          |

| Figure 2-12 Components encapsulated in the BCM47511 chip       31         Figure 3-1 Layout of components on the S10 PCBA       32         Figure 4-1 Functional blocks of the PCBA       38         Figure 4-2 Layout of components on the PCBA       38         Figure 4-3 Physical architecture of the PCBA       39         Figure 4-4 Power-on and power-off sequencing       40         Figure 4-5 Power-on procedure       41         Figure 4-6 AP framework       42 |

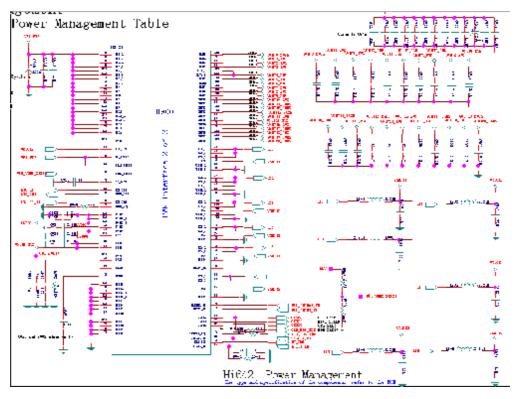

| Figure 2-12 Components encapsulated in the BCM47511 chip31Figure 3-1 Layout of components on the S10 PCBA32Figure 4-1 Functional blocks of the PCBA38Figure 4-2 Layout of components on the PCBA38Figure 4-3 Physical architecture of the PCBA39Figure 4-4 Power-on and power-off sequencing40Figure 4-5 Power-on procedure.41Figure 4-6 AP framework42Figure 4-7 Working principles of the PMU.45                                                                            |

# **Tables**

| Table 1-1 External hardware interfaces                            |

|-------------------------------------------------------------------|

| Table 1-2 Hardware specifications of the MediaPad 10 FHD       11 |

| Table 3-1 Description of components on the S10 PCBA    32         |

| Table 4-1 Voltage signals of the AP power circuit    45           |

| Table 4-2 Possible faults of the AP power circuit    47           |

| Table 4-3 Definitions of signals of the AP charging circuit       |

| Table 4-4 Definitions of signals of the coulometer circuit        |

| Table 4-5 Definitions of signals of the eMMC circuit    52        |

| Table 4-6 Definitions of signals of the MIC circuit    53         |

| Table 4-7 Definitions of signals of the headset circuit           |

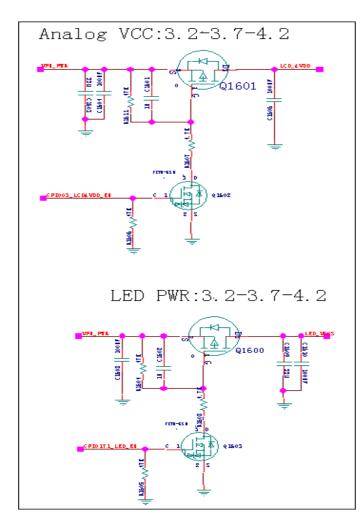

| Table 4-8 Definitions of signals of the LCD circuit               |

| Table 4-9 Definitions of signals of the TP circuit    58          |

| Table 4-10 Definitions of signals of the camera circuit    60     |

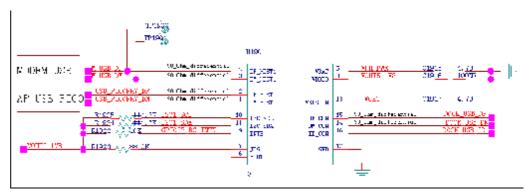

| Table 4-11 Definitions of signals of the BC1.1 circuit            |

| Table 4-12 Definitions of signals of the charging circuit    63   |

| Table 4-13 Definitions of signals of the sensor circuit           |

| Table 5-1 Upgrade preparation   73                                |

| Table 7-1 Test spot list   78                                     |

# **Product Overview**

# **1.1 Brief Introduction**

#### Background

10-inch tablets take a share of more than 70% of the tablet market. As a mainstream model of tablets, they provide Internet surfing, pleasant visual experience, and portable use. 10-inch tablets have found their way in a variety of application fields, such as retailing, operators' mobile broadband product reselling, operators' promotion of new home products, enterprise office administration, and financial insurance.

MediaPad 10 FHD is a 10-inch tablet of Huawei MediaPad series based on the Android 4.0 (Ice Cream Sandwich) operating system. Its hardware integrates an access point (AP) and a modem (K3+BalongV7). Equipped with a 10.1-inch in-plane switching (IPS) thin-film transistor (TFT) LCD, the MediaPad 10 FHD features high resolution (1920 x 1200 pixels) and provides complete touchscreen operations. It supports multiple audio and video formats, such as MP3, MP4, AVI, ASF, and WAV.

The MediaPad 10 FHD also provides the following auxiliary functions:

- I 8.0 megapixel (MP) camera

- I microSD card

- I Global positioning system (GPS)

- Wireless Fidelity (Wi-Fi)

- I Bluetooth 4.0

- I Frequency modulation (FM)

- I Acceleration sensor

- I Proximity sensor

- I Light sensor

- I Gyroscope sensor

- I Compass

- I Electromagnetic sensor

In terms of wireless communication, the MediaPad 10 FHD supports the following features:

- I GSM mode: GPRS and EDGE

- WCDMA mode: UMTS, HSDPA, and HSPA+

- WCDMA frequency bands: bands 1, 2, 5, 8, 9, and 11

- GSM frequency bands: 850 MHz, 900 MHz, 1800 MHz, and 1900 MHz.

The entire device has five antennas: one host antenna, one diversity antenna, one GPS antenna, one antenna for the Bluetooth and Wi-Fi modules, and one independent antenna for the synthetic aperture radar (SAR) sensor.

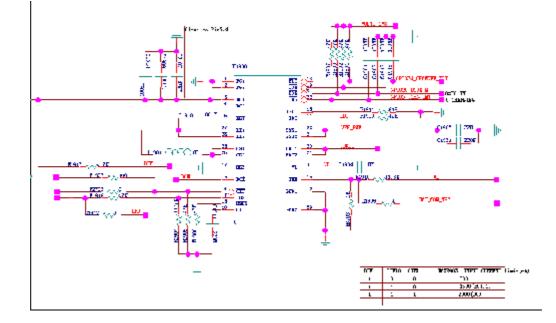

The smart chip MAX8903 is used for charging management, the Broadcom BCM4330 chip is used for the Wi-Fi and Bluetooth modules, and the BCM47511 chip is used for the GPS module.

The MediaPad 10 FHD has the following memory features:

- AP RAM: LP DDR2, standard 1 GB 533 Hz (compatible with 2 GB)

- AP ROM: eMMC, standard 8 GB (compatible with 16 GB and 32 GB)

- Modem: Hi6920+Hi6451+Hi6360, MCP (NAND+DDR), standard 2 Gbit + 1 Gbit (compatible with 1 Gbit + 512 Mbit)

The MediaPad 10 FHD supports the 3.5 mm headset jack and 30-pin dock interface. The dock interface supports multiple functions, such as charging, power supply, USB host or device installation, and the display port.

Figure 1-1 shows the appearance of the MediaPad 10 FHD.

#### Figure 1-1 Appearance of the MediaPad 10 FHD

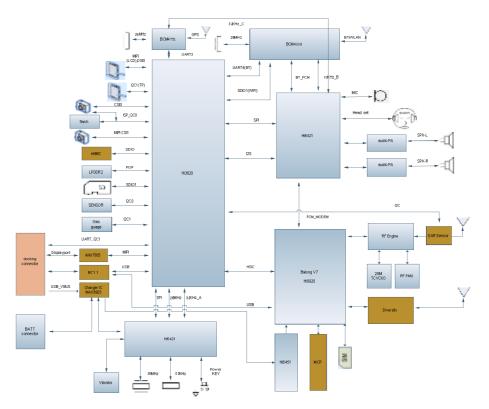

Figure 1-2 shows the hardware principles of the MediaPad 10 FHD (Hi3620+Hi6920).

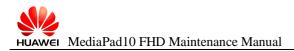

Figure 1-2 Hardware principles of the MediaPad 10 FHD

#### **Board Functions**

The main control board provides the following functions:

- Provides the host CPU and processes image signals.

- I Manages host power supply.

- Supports UMTS (WCDMA), HSPA, GSM, GPRS, and EDGE.

- I Supports GPS.

- Provides LCD and camera interfaces.

- I Provides audio interfaces.

- Provides a WLAN or Bluetooth module.

The interface board provides the following functions:

- I Provides dock interfaces.

- Provides USB and charging interfaces.

Table 1-1 lists the hardware interfaces provided by the MediaPad 10 FHD.

| No. | Interface<br>Type | Physical<br>Interface Mode         | Number of<br>Interfaces | Remarks                                                                                                  |

|-----|-------------------|------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------|

| 1   | USB               | OTG                                | 1                       | This interface is used to connect to a PC or other devices. It complies with the USB 2.0 specification.  |

| 2   | 3G                | Main antenna and diversity antenna | 2                       | This interface is an uplink data interface for voice services (WCDMA).                                   |

| 3   | WLAN              | Built-in antenna                   | 1                       | This interface is used to connect to a local WLAN device.                                                |

| 4   | Dock<br>interface | Dock jack                          | 1                       | This interface provides numerous<br>communication signals, such as power input,<br>MHL, and USB signals. |

| 5   | Power switch      | Tact switch                        | 1                       | Power switch                                                                                             |

| 6   | Key               | Sound volume<br>adjustment key     | 2                       | VOL+, VOL-                                                                                               |

| 7   | Touchscreen       | Capacitor screen,<br>I2C interface | 1                       | Compatible with the resistor-capacitor                                                                   |

| 8   | LCD               | MIPI                               | 1                       | 1920 x 1080 pixels                                                                                       |

| 9   | JTAG<br>interface | Normalized 9-pin<br>encapsulation  | 1                       | This JTAG interface is used for program loading.                                                         |

| 10  |                   |                                    |                         |                                                                                                          |

| 11  |                   |                                    |                         |                                                                                                          |

| 12  |                   |                                    |                         |                                                                                                          |

| 13  |                   |                                    |                         |                                                                                                          |

#### Table 1-1 External hardware interfaces

# **1.2 Hardware Specifications**

Table 1-2 lists the hardware specifications of the MediaPad 10 FHD.

| Table 1-2 Hardware specifications of the MediaPad 10 FHD |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Technical Parameter    | Specification                |

|------------------------|------------------------------|

| Dimensions (H x W x D) | 8.9 mm x 267.2 mm x 169.8 mm |

| Weight                 | About 630 g (TBD)            |

| Technical Parameter | Specification                                                                                                                        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Shape               |                                                                                                                                      |

| Battery             | 6300 mA                                                                                                                              |

| Display             | 10.1-inch WXGA (1920 x 1200 pixels), TFT, touchscreen                                                                                |

| Touch panel         | Capacitive, Multi-touch (10 points)                                                                                                  |

| Interface           | <ul><li>30-pin dock connector</li><li>3.5 mm headset jack</li></ul>                                                                  |

| Band                | S10-101u: UMTS 2100/900, EDGE/GPRS/GSM (850/900/1800/1900)           S10-102u: UMTS 2100/1900/850, EDGE/GPRS/GSM (850/900/1800/1900) |

|                     | HSPA+: 42 Mbit/s                                                                                                                     |

| Chipset             | Hi3620T (K3 V2) + Hi6920 (Balong V7)                                                                                                 |

| OS                  | Android 4.0 (Ice Cream Sandwich)                                                                                                     |

| Memory              | RAM: 2 GB<br>ROM: 16 GB<br>Maximum 32 GB microSD card                                                                                |

| Multimedia          | Rear camera: 8.0 MP HD AF, dual LED flash<br>Front camera: 1.3 MP HD<br>H.263, MPEG4, H.264 (decode)<br>MP3, AAC, AAC+               |

| Network service     | 3G                                                                                                                                   |

| Others              | Wi-Fi b/g/n, Bluetooth v3.0 +HS, DLNA, 30-pin dock connector, 1080p video                                                            |

# **1.3 Software Specifications**

# 1.4 Exploded View of the Host

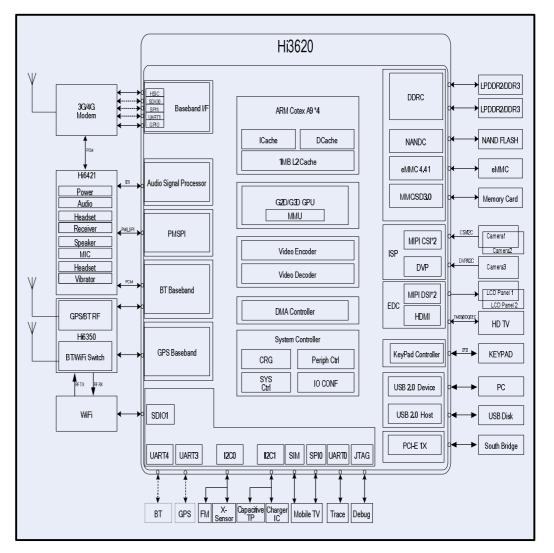

Figure 1-3 shows the exploded view of the host.

# **2** Functional Chips

## 2.1 Hi3620

The Hi3620 is a new-generation quad core ARM cortex-A9 processor launched by Hisilicon. The processor supports 1.2 GHz processing.

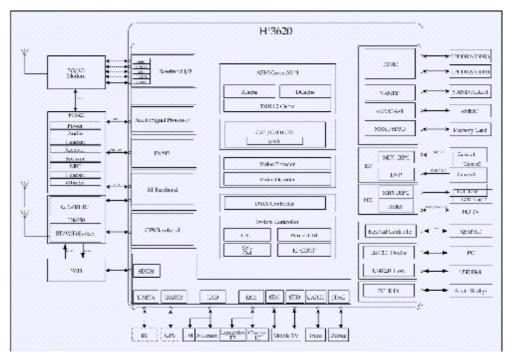

Figure 2-1 shows the functional blocks of the Hi3620.

Hi3620 Cortex A9 SMP Nand Flash MIPI-Port MIPI DSI\*2 Enhanced 4 Core Video LCD Panal Mobile DDR LP DDR2 🔸 Display Decoder Controller ICache DCache Controller HDMI TV WIFI/ SDIO PTM NOEN Modem Controller \*2 Video 2D/3D GPU MIPI-Port SD Card 🔸 SD Controller ISP/MIPI CSI\*2 Encdoer 1MB L2 Cache MMU Camera Audio Signal Core Controller System Controller Modem →HSIC PHY DMAC Processor SYS Hi6421 CRG TIMER \* 10 CTRL USB FS PMUSPI USB HS USB Host PERIPH Device PHY VIC PWM PMU GPIO \* 22 CTRL USB 2.0 USB USB WD RTC ю Device AVS eMMC PICO -Device CONF eMMC PHY Controller controller PCIE UART\*5 GPS KPC I2C 1 HSIC SPI 2 12C 2 ΒT ŧ ¥ Mobile LTE Wireless SATA FΜ RF KeyPad Modem TV Modem

Figure 2-1 Functional blocks of the Hi3620

## 2.1.1 Chip Specifications

Encapsulation: 11.90 mm x 11.90 mm, 576-pin BGA/CSP encapsulation, Hi3620 (IC).

## 2.1.2 Pin Assignment

## 2.1.3 Working Principles and Functions of the Hi3620

The K3V200 system uses the Hi3620 chip as its core to provide the following logical interfaces:

#### NAND/eMMC Interface

The Hi3620 provides 16-bit NAND interfaces. The high 8-bits are multiplexed with the eMMC interface. Therefore, it is recommended that the eight high-order bits be connected to the eMMC component and the eight low-order bits be connected to a component such as the MLC NAND or Clear NAND.

#### **Camera Interface and LCD Interface**

The Hi3620 provides three MIPI interfaces: CSI0, DSI0, and CSI\_DSI1. Each interface can contain four data lanes. The Hi3620 also provides one parallel camera interface which is known as the DVP interface.

- CSI0: This interface is used for camera image capturing.

- DSI0: This interface is used for LCD display.

- CSI1\_DSI1: This interface can be statically multiplexed as an LCD display interface (in the two-screen application scenario) or as an interface for camera image capturing (in 3D image pickup and master/master camera application scenarios).

- DVP: This interface is used to connect to a camera through a parallel bus. It is reserved for the front camera.

#### microSD Card Interface

The Hi3620 provides a dedicated microSD card slot, which complies with the SD3.0 specification and supports the SDR50 or DDR50.

####

The bus clock frequency of the SDR50 is 100 MHz, and that of the DDR50 is 50 MHz.

#### **SDIO Interface**

The Hi3620 provides two SDIO buses, which comply with the SD2.0 specification and support at most the SDR25. The two buses are used to connect peripherals.

- SDIO0: This interface is the data and control interface of the AP or modem. Its signal level is 1.8 V or 2.5 V.

- SDIO1: This interface is the data and control interface of Wi-Fi. Its signal level is 1.8 V.

####

The bus clock frequency of the SDR25 is 50 MHz.

#### **UART Interface**

The Hi3620 provides five UART interfaces, all of which support four-wire hardware flow control and provide the maximum baud rate of 3.25 Mbit/s. These interfaces are used to connect to peripherals.

- UART0: This UART interface is specially used for system commissioning or loading. Its signal level is 2.5 V.

- UART1: This interface is used as the data and control interface of the AP or modem. It can also be multiplexed as a GPIO interface. Its signal level is 1.8 V or 2.5 V.

- UART2: This interface is statically multiplexed with USIM and onewire signals and reserved for peripherals. Its signal level is 1.8 V.

- UART3: This interface is multiplexed with the GPS baseband bus GPS\_SPI that is integrated in the Hi3620. It provides a data and control channel for external third-party GPS devices. Its signal level is 1.8 V.

- UART4: This interface is multiplexed with the Bluetooth baseband interface BT\_IF that is integrated in the Hi3620. It provides a data and control channel for external third-party Bluetooth devices. Its signal level is 1.8 V.

#### **SPI Interface**

The Hi3620 supports five groups of SPI bus interfaces, all of which work in master mode.

- SPI0: This SPI interface supports a maximum of four chip selection signals. It is reserved for peripherals, such as the CMMB. Its signal level is 1.8 V.

- SPI1: This interface is the communication and control interface of the modem. Its signal level is 1.8 V or 2.5 V.

- PMU\_SPI: This SPI interface is dedicated for the PMU (Hi6421) and works in three-wire mode (the input end and the output end share the same data signal). Its signal level is 1.8 V.

- BT\_SPI: This interface is a dedicated SPI interface between a Bluetooth baseband unit integrated in the Hi3620 and the RF IC (Hi6350). Its signal level is 1.8 V.

- GPS\_SPI: This interface is a dedicated SPI interface between a GPS baseband unit integrated in the Hi3620 and the RF IC (Hi6350). Its signal level is 1.8 V.

#### I2C Bus

The Hi3620 provides four groups of I2C buses. Two groups are dedicated for camera interfaces, and the other two groups are used for peripherals.

- I ISP\_I2C0/1: used for camera I2C interfaces.

- I I2C0: used for the xSenor, capacitive touchscreen, and independent FM communication and data interfaces.

- I I2C1: used for the charging IC.

####

The xSensor and capacitive touchscreen are components that may be frequently accessed. Therefore, the preceding I2C bus allocation mode is applied by default but a jumper is reserved during design to connect the capacitive touchscreen to I2C1.

#### **Digital Audio Interface PCM/I2S**

The K3V200 system provides three groups of digital audio interfaces to connect to a codec inside the Hi6421.

- I I2S interface: This interface is a stereo audio interface between the Hi3620 and the codec inside the Hi6421.

- M\_PCM interface: This interface provides a voice channel between the modem and the codec inside the Hi6421.

BT\_PCM interface: This interface provides a voice channel between external third-party Bluetooth devices and the codec inside the Hi6421.

#### HDMI Interface

The Hi3620 complies with the HDMI1.3a protocol specification. It supports high-definition playing (up to 1080p) and provides HDMI interfaces to connect to external display devices.

#### **HSIC Interface**

The Hi3620 provides the HSIC interface as the active high-rate communication and control interface between the AP and the modem.

#### **USB** Interface

The Hi3620 provides two USB2.0 interfaces, both of which support the highest speed 480 Mbit/s.

- USB\_NANO interface: This interface statically supports USB 2.0 hosts and devices.

- USB\_PICO interface: This interface supports USB2.0 devices and BC1.1 (in compliance with a charging specification supplementary to the USB2.0 specification).

#### **PCIe Interface**

The Hi3620 supports one PCIe 1.0 interface, which is reserved for external devices, such as a South Bridge or SATA disk.

### 2.2 POP LPDDR2

The DDR2 chip uses the POP encapsulation technology. Currently, two vendors ELPIDA and Samsung supply this chip to Huawei.

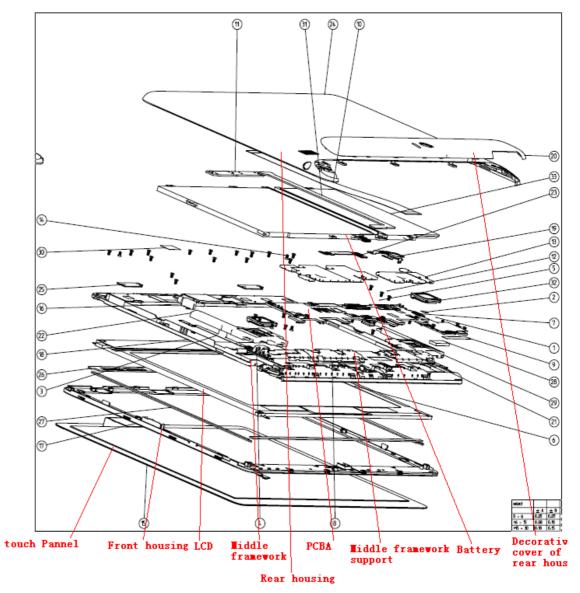

Figure 2-2 shows the functional blocks of the POP LPDDR2 chip.

#### Figure 2-2 Functional blocks of the POP LPDDR2 chip

Figure 2-3 shows the model of the POP LPDDR2 chip provided by ELPIDA.

| Part number      | Organization<br>(words x bits) | Clock frequency | Data rate | Read latency | Package                                                     |  |

|------------------|--------------------------------|-----------------|-----------|--------------|-------------------------------------------------------------|--|

| EDB8164B3PF-1D-F | 128M x 64                      | 533MHz          | 1066Mbps  | 8            |                                                             |  |

| ED88164B3PF-8D-F | (128M × 32 × 2pcs)             | 400MHz          | 800Mbps   | 6            |                                                             |  |

| Elpida Memory    |                                |                 |           |              | onment Code<br>Lead Free (RoHS complian<br>and Halogen Free |  |

Figure 2-4 shows the model of the POP LPDDR2 chip provided by Samsung.

| Part Number                                                                         | Max                    | Max Freq.              |                                |                                                             |  |

|-------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------------|-------------------------------------------------------------|--|

| Part Number                                                                         | A-Channel              | B-Channel              | Interface                      | Package                                                     |  |

| K3PE7E700M-XGC1                                                                     | 800Mbps (tCK=2.50ns)   | 800Mbps (tCK=2.50ns)   |                                | 12x12 216FBGA<br>(Lead Free, Halogen Free)                  |  |

| K3PE7E700M-XGC2                                                                     | 1066Mbps (tCK=1.875ns) | 1066Mbps (tCK=1.875ns) | HSUL_12                        |                                                             |  |

| Samsung<br>Mobile DRAM Stack Memory                                                 | <u>K3 P E7 E7</u>      | <u>00M-XG</u>          | Speed<br>C1:2.5ns(             | gRL6, IRCD18ns, IRP18ns<br>ins@RL8, IRCD18ns, IRP18ns       |  |

| Device Type<br>P : LPDDR2-S4 + LPDDR2-S4                                            | 4                      |                        | G :<br>Pa                      | np.<br>-25 ∼ 85°C<br>ckage<br>FBGA (Lead Free, Halogen Free |  |

| Ch.A Density, Organizatio<br>E7 : LPDDR2-S4 4Gb, VDD1=<br>VDDQ=1.2V, VDDCA=1.2V, x2 | 1.8V, VDD2=1.2V,       |                        | Ge                             | neration<br>1st Generation                                  |  |

|                                                                                     |                        |                        |                                | erposer I/F<br>None                                         |  |

| Ch.B Density, Organizatio<br>57 : LPDDR2-S4 4Gb, VDD1=<br>VDDQ=1.2V, VDDCA=1.2V, x3 | 1.8V, VDD2=1.2V,       | 10                     | C-Port I/F &<br>0 : Reserve to | Density & VCC & Org.                                        |  |

#### Figure 2-4 Model of the POP LPDDR2 chip provided by Samsung

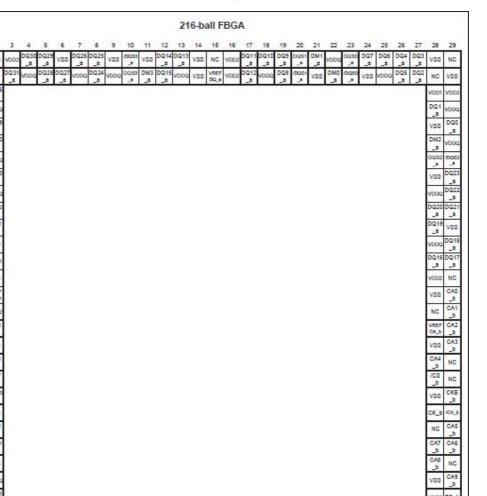

Figure 2-5 shows the pin assignment of the POP LPDDR2 chip.

#### Figure 2-5 Pin assignment of the POP LPDDR2 chip

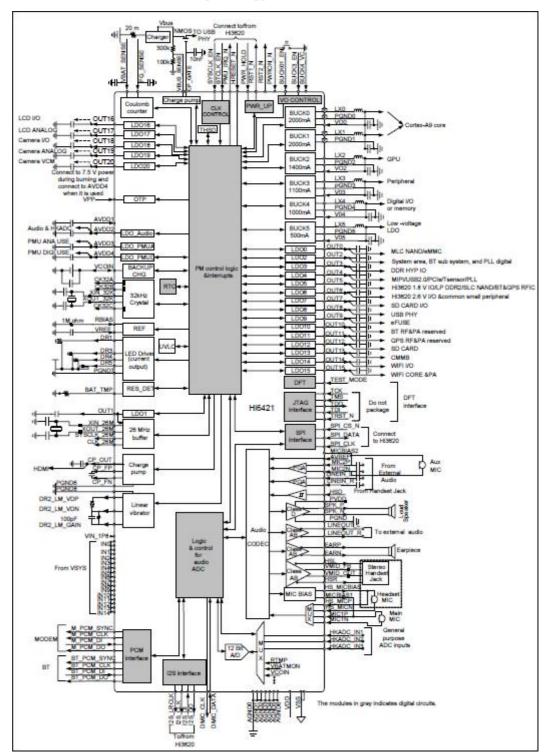

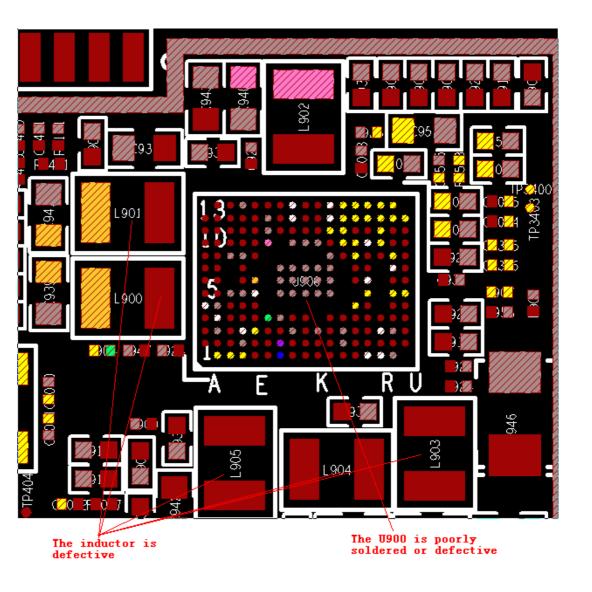

## 2.3 PMU Hi6421

The Hi6421V200 chip is an important component of Hisilicon K3 application processor solution, which is a semiconductor solution for mobile phones. It is an integrated circuit that provides power management, audio processing, and diversified interfaces. Its functions are described as follows:

#### **Power Supply**

BUCK0 and BUCK1 serve as the primary power of the quad core A9, and output 1.1 V by default. The maximum parallel output current is 4000 mA. BUCK0 and BUCK1 are switched on or off by controlling the external hardwire signal BUCK01\_EN. The output voltage is adjusted through SPI interfaces to meet the system AVS policy, so that the power consumption of the system is minimized on the precondition of guaranteed system performance.

INTERNAL

VRS

BUCK2 serves as the primary power of the GPU, and outputs 1.1 V by default. Its maximum current is 1400 mA. SPI interfaces are applied to switch on or off BUCK2 and adjust the output voltage of BUCK2, so that the power consumption of the system is effectively controlled.

BUCK3 supplies power to the peripherals of the Hi3620, and outputs 1.1 V by default. Its maximum current is 1100 mA. BUCK3 is switched on or off by controlling the external hardwire signal BUCK3\_EN.

BUCK4 supplies power to the I/O of the Hi3620 (by default the power voltage is 1.8 V) or the LP DDR2 (by default the power voltage is 1.2 V). Its maximum current is 1000 mA. The default output voltage varies according to different applications. The default output voltage is controlled by the external hardwire signal BUCK4\_VC.

BUCK5 serves as the input power of LDO2 and LDO3 to improve the operating efficiency of low dropout (LDO) regulators. Its maximum current is 500 mA.

Of the 24 LDOs, 21 LDOs supply power to the following components:

- I MLC NAND

- I 26 MHz clock oscillation circuit

- I AP system area

- I DDR HPY I/O

- I MIPI

- I 3620 and Hi6421V200 digital I/O

- I 3620 2.6 V I/O

- I microSD card I/O

- I USB PHY

- l eFuse

- I Bluetooth

- I GPS

- I microSD card

- I CMMB

- I Wi-Fi I/O

- I Wi-Fi core

- I LCD I/O

- LCD analog

- I Camera I/O

- I Camera analog

- I Camera VCM

All these power channels support power saving (in dormant or ECO mode). The rest three LDOs supply power to an audio circuit (including HKADC), a PMU analog circuit, and a PMU digital circuit. The charge pump supplies power to the HDMI, and provides the backup battery charging function.

#### Audio Unit

The audio unit integrates a sigma-delta audio codec, which makes possible flexible resource configuration and provides abundant audio applications to meet audio processing

requirements in various scenarios. The Hi6421V200 chip can connect to the AP, modem, or Bluetooth through one I2S interface and two PCM digital audio interfaces. It can also connect to peripherals through analog interfaces, such as line I/O and MIC interfaces.

Furthermore, the audio unit implements interworking and switching between audio signal resources, provides sound volume adjustment, and supports digital MIC input signals. Multiple audio amplifiers are built in the Hi6421V200 chip to drive the loudspeaker, headset, and earpiece. The headset checking function is used to identify whether the headset is installed. It helps the system save power overheads, and supports headset key detection.

#### Interface Unit

The interface unit of the Hi6421V200 chip provides the following functions:

- Uses SPI interfaces to implement high-rate communication with the AP

- Provides a coulometer to detect changes to the electric energy of the battery

- Provides a 12-bit HKADC to monitor four channels of analog parameters in real time, including the voltage of the main battery, the temperature of the main battery, and the voltage of the backup coin battery.

- Provides the drive for one vibration motor or linear motor, one LED background drive (maximum current 40 mA), and three LED drives (the breathing function can be configured)

- Provides one 26 MHz clock oscillator and two output drives.

- Provides one 32.768 kHz clock oscillator and three output drives.

- Provides one interface circuit for detecting the thermistor of the main battery.

Figure 2-6 shows the functional blocks of the power supply.

The Hi6421V200 chip has the following features:

Five high-efficiency buck-type switch power convertors

BUCK0: 1.1 V 2000 mA for the A9 Core, supporting AVS adjustment.

BUCK1: 1.1 V 2000 mA for the A9 Core, supporting AVS adjustment.

BUCK2: 1.1 V 1400 mA for the GPU, supporting AVS adjustment.

BUCK3: 1.1 V 1100 mA for peripherals.

BUCK4: 1.2 V or 1.8 V 1000 mA for LPDDR2 or AP I/O.

BUCK5: 1.8 V 500 mA for low-voltage LDO.

####

BUCK0 and BUCK1 are connected in parallel.

1 21 external LDO linear voltage regulators and four internal LDO linear voltage regulators

LDO0: 2.85 V @ 300 mA for MLC NAND/eMMC

LDO1: 1.8 V @ 50 mA for 26 MHz clock oscillation circuit

LDO2: 1.1 V @ 150 mA for the system area, Bluetooth subsystem, and digital PLL (The system in standby mode does not need to be powered off)

LDO3: 1.2 V @ 350 mA for the DDR PHY I/O to be powered off or the HSIC PHY 1.2 V (Power-off is required)

LDO4: 2.5 V @ 250 mA for MIPI/USB2.0/PCIe/T Sensor/PLL 2.5 V analog power (Power-off is required)

LDO5: 1.8 V @ 300 mA for Hi3620 & Hi6421V200 1.8 V I/O, LP DDR2, SLC NAND, or Bluetooth&GPS RFIC

LDO6: 2.6 V @ 300 mA for Hi3620 2.6 V I/O and small peripherals

LDO7: 2.6 V @ 50 mA for Hi3620 microSD card slot I/O (Dynamic switching between 1.8 V and 2.6 V is needed)

LDO8: 3.3 V @ 200 mA for USB PHY

LDO9: 2.6 V @ 200 mA for eFuse power supply (Power-off is required)

LDO10: 2.85 V @ 150 mA for Bluetooth RF&PA; reserved

LDO11: 2.85 V @ 150 mA for GPS RF&PA; reserved

LDO12: 2.85 V @ 500 mA for the microSD card

LDO13: 2.85 V @ 300 mA for CMMB

LDO14: 2.85 V @ 150 mA for Wi-Fi I/O

LDO15: 3.3 V @ 300 mA for Wi-Fi core&PA

LDO16: 2.85 V @ 150 mA for LCD I/O

LDO17: 2.85 V @ 150 mA for LCD Analog

LDO18: 2.85 V @ 300 mA for Camera I/O and the input of the internal core power regulator

LDO19: 2.85 V @ 300 mA for LCD Camera Analog

LDO20: 2.85 V @ 300 mA for LCD Camera VCM

LDO\_Audio: 3.3 V @ 300 mA for Audio & HKADC

LDO\_PMUA: 3.15 V @ 10 mA for PMU Analog

LDO\_PMUD: 1.8 V @ 10 mA for PMU Digital

Real-time clock (RTC) with the alarm clock function

The Hi6421V200 chip integrates a 32.768 kHz crystal oscillator and supports three channels of clock buffer output independently controlled.

The RTC serves as the reference time and date benchmark of the system.

The RTC supports the alarm clock function and scheduled power-on.

The RTC supports power supply through a backup coin battery.

I.

- Two channels of 26 MHz high-frequency clock drive and output The Hi6421V200 chip integrates a 26 MHz clock oscillator drive. The Hi6421V200 chip is compatible with 26 MHz input clocks.

- Two channels of independent 26 MHz clock buffer output

- Four LED DC drive ports

DR1 can be used for keypad backlight control. The drive current ranges from 5 to 40 mA.

DR3 maps to a red LED, DR4 maps to a green LED, and DR5 maps to a blue LED. They support breath control.

I One DC or linear motor drive

DR2 supports strong drive capability up to 250 mA.

- I Three-wire SPI interfaces to communicate with the processor

- I One charge pump boost converter

The boost converter outputs a 5 V voltage and a maximum of 60 mA current.

Built-in 12-bit HKADC to monitor physical status parameters in real time The 12-bit HKADC can detect the voltage of the battery.

The 12-bit HKADC can detect the voltage of the coin battery.

The 12-bit HKADC can detect the three channels of external analog input voltages.

The 12-bit HKADC can detect the testability of other signals inside the chip.

- I Detecting changes to the electric energy of the battery by using a coulometer

- I Complete audio processing solution

- Supporting normal system power-on and operations when the main battery is not detected

- I Low-power design

The entire operating current of the chip is only 150 uA (typical value for the system in dormant state) or 30 uA (when the system is powered off and only the RTC is working).

- I Over-voltage, over-heat, and over-current protection

- I Operating temperature:  $-30^{\circ}$ C to  $+85^{\circ}$ C

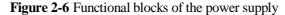

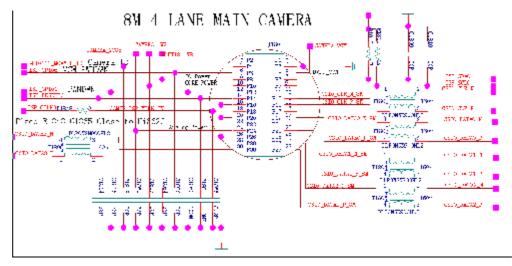

## 2.4 Wi-Fi and Bluetooth Modules

The Wi-Fi and Bluetooth modules of the S10 are designed based on the integrated chip BCM4330 according to Huawei principle of normalization for Wi-Fi design. The BCM4330 chip integrates the IEEE 802.11b/g/n 2.4 GHz or 5.1 GHz solution (RF transceiving and baseband demodulation) and a transceiver for the Bluetooth and FM modules. Signals from the Bluetooth and FM modules are output by the transceiver of the BCM4330 chip to the Hi6421 modulation and demodulation module on the AP side to implement the overall functions of the BCM4330 chip. The BCM4330 chip can use external Wi-Fi power amplifiers (PAs) or low-noise amplifier (LNAs) to improve Wi-Fi RF performance and provide higher expandability. In particular, an external PA or LNA can be deployed in subsequent version planning to improve Wi-Fi power and sensitivity to meet strict Wi-Fi RF performance requirements of TMO in North America.

In terms of RF design for Wi-Fi, Bluetooth, and FM modules, the 2.4 GHz frequency band is applied to Wi-Fi and Bluetooth modules. Both Wi-Fi and Bluetooth work in time division duplex (TDD) mode and transmit or receive signals on the same antenna under switch control.

For the FM module, a common earphone antenna is used to receive FM signals. The BCM4330 chip performs intermediate frequency (IF) conversion for FM signals, so that IF signals are demodulated on the AP side.

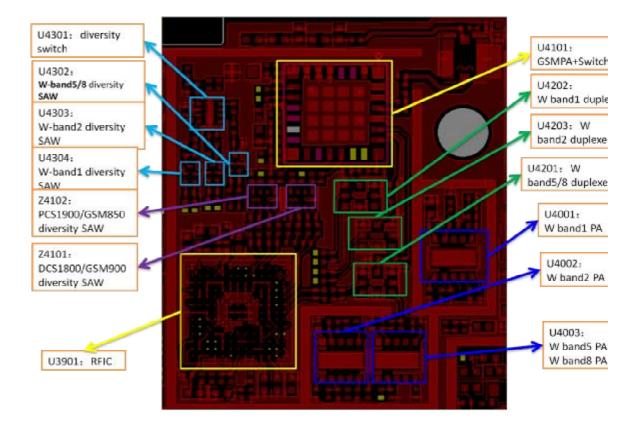

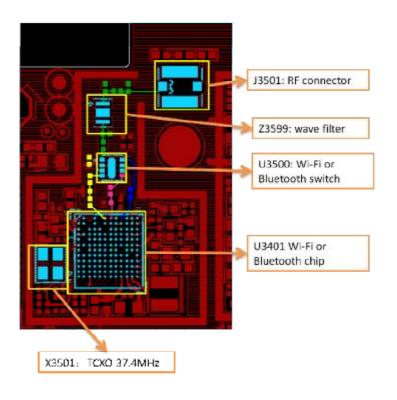

Figure 2-7 shows the RF solution for the Wi-Fi and Bluetooth modules of the S10.

Figure 2-7 RF solution for the Wi-Fi and Bluetooth modules of the S10

Figure 2-8 shows the components encapsulated in the WI-FI or Bluetooth module.

#### Figure 2-8 Components encapsulated in the WI-FI or Bluetooth module

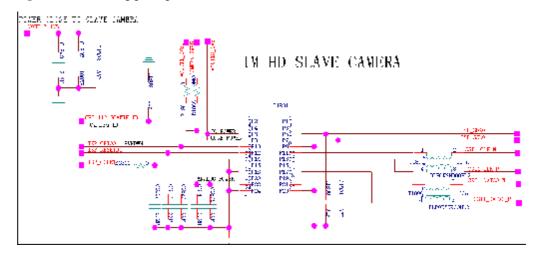

### 2.5 GPS BCM47511

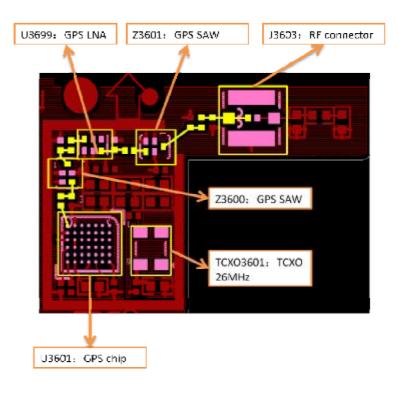

The S10 needs to include a GPS module to implement the GNSS function. It must also be compatible with the global navigation satellite system (GLONASS). Therefore, Huawei selected the GPS chip BCM47511. The BCM47511 chip provides external GPS LNA interfaces to improve the receiving performance of the GPS module.

Figure 2-9 shows the functional blocks of the RF solution for the GPS module of the S10. After the GPS antenna receives signals from the GPS or GLONASS, SAW filtering is

performed before signals are amplified by an LNA. Then SAW filtering is performed again before signals are input to the BCM47511 for further processing.

#### Figure 2-9 RF solution for the GPS module of the S10

The BCM47511 chip has the following features:

- I The BCM47511 SoC solution uses an independent new-generation GPS receiver developed by Broadcom. This GPS receiver integrates the functions of both the GPS and the GLONASS. The BCM47511 chip is compatible with pins in the popular BCM4751 SoC solution launched by Broadcom. Therefore, customers can quickly upgrade products to support the GLONASS.

- I The GPS kernel of the BCM47511 chip, based on a host system architecture, splits the processing function into two parts which are separately implemented by the GPS chip and the main system CPU. This obviously reduces system costs. In addition, the GPS or GLONASS software algorithm used on the main system can be customized or optimized when necessary. After splitting the processing function into two parts, the GPS receiver of the BCM47511 chip can perform most dense computation tasks, so that the software on the main system needs only to perform the ultimate calculation.

- I The BCM47511 chip consumes little power and provides an ultra-low-power tracing mode. It integrates LDO voltage regulators to provide a temperature-compensated crystal oscillator (TCXO) for the GNSS. The BCM47511 chip can also have LNAs to lower the total material cost. Broadcom provides GPS location library APIs and GPS protocol client software, so that designers can make full use of the advanced functions of the BCM47511 chip.

- I The Bluetooth kernel of the BCM47511 chip is optimized to attain low power consumption. This kernel also maintains high receiver sensitivity and complies with the Bluetooth 4.0 specification.

Figure 2-10 shows the functional blocks of the BCM47511 chip.

Figure 2-10 Functional blocks of the BCM47511 chip

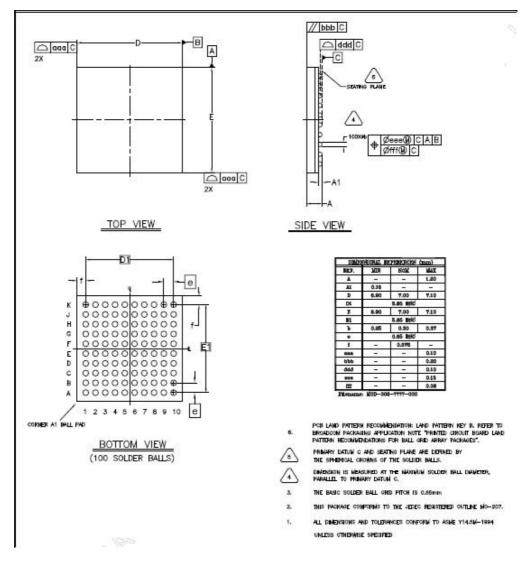

Figure 2-11 shows the available models of the BCM47511.

Figure 2-11 Models of the BCM47511

| Part Number                | Package      | Packing       | Minimum Order Quantity |

|----------------------------|--------------|---------------|------------------------|

| BCM47511IFBG               | 100-pin FBGA | Tape-and-reel | 2,500                  |

| BCM47511IUBG               | 42-pin WLBGA | Tape-and-reel | 5,000                  |

| BCM47511IUB2G <sup>a</sup> | 42-pin WLBGA | Tape-and-reel | 5,000                  |

Figure 2-12 shows the components encapsulated in the BCM47511 chip.

#### Figure 2-12 Components encapsulated in the BCM47511 chip

# **3** Layout of Major Components

# 3.1 Layout of Components on the S10 PCBA

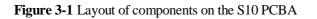

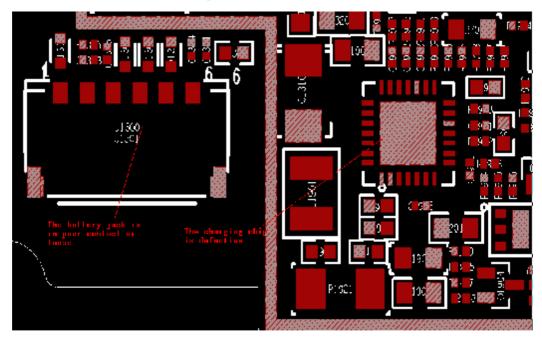

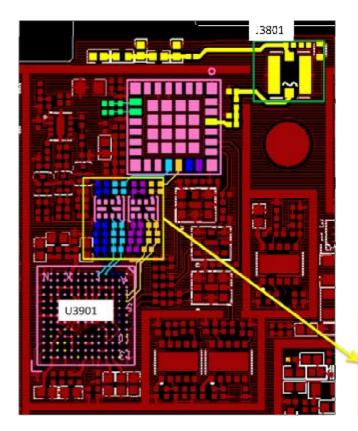

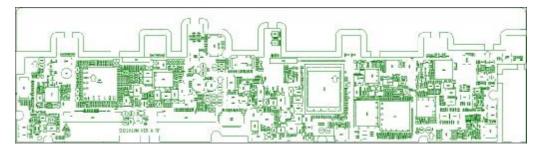

Figure 3-1 shows the layout of components on the S10 PCBA.

# **3.2 Components on the S10 PCBA**

Table 3-1 lists the components on the S10 PCBA.

Table 3-1 Description of components on the S10 PCBA

| BOM Number | Description                                                                 | Remarks |

|------------|-----------------------------------------------------------------------------|---------|

| 14240181   | BTB Connector,Fmale,24Pin,0.4mm,SMT,Mating Height 1.0 mm,Terminal Dedicated | J2105   |

| BOM Number | Description                                                                                                                              | Remarks                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 14090087   | Soft Print Board Connector,40Pin,0.5mm,0.5mm,0.3mm,Term inal Dedicated                                                                   | J2301                                                                                            |

| 39210010   | Terminal Baseband process IC,Single Band 2.4GHz WLAN/<br>Bluetooth 2.1/FM Single chip-BCM4330,2.3~5.5V,WLBGA1<br>33(Pb-free)             | U3401                                                                                            |

| 35020160   | Consumption Chip,Hi3620GFCV111G12,FCCSP 576,1.1/1.2/<br>1.8/2.6/3.3V,Application processor                                               | U300                                                                                             |

| 40020172   | DDR2 DRAM,8Gb LPDDR2,533MHz,32bit,1.8V/1.2V,216B<br>ALL FBGA(POP),Terminal Dedicated                                                     | U300_POP                                                                                         |

| 35020158   | Consumer Chips-Hi6421GFCV231-FCCSP189-1.8/3.3/4.2V-K<br>3 PMU and Codec chip                                                             | U900                                                                                             |

| 14240470   | Card Block Connector,female,40,0.4mm,Micro Coaxial Conn<br>ector,Terminal Dedicated                                                      | J1601                                                                                            |

| 38140024   | Semiconductor Sensor,E-Compass,WL-CSP(Pb-free),3axis,Ter<br>minal Dedicated                                                              | U2005                                                                                            |

| 38140020   | Semiconductor Sensor, three-axis gyroscope, SMT                                                                                          | U2003                                                                                            |

| 38140023   | Semiconductor Sensor, Accelerometer, LGA, 3axis, Terminal De dicated                                                                     | U2003                                                                                            |

| 51621274   | DKBA8.382.0615,Main Antenna SMT Spring,C5600                                                                                             | J100, J1000,<br>J1001, J1002,<br>J1003, J3503,<br>J3504, J3601,<br>J3602, J3802,<br>J3804, J3805 |

| 14240533   | IO Connector,WTB Connector,6pin,single row,Terminal Dedi cated                                                                           | J1301                                                                                            |

| 39070073   | -0.3~2.75V,Battery Gauge,SON,Terminal Dedicated                                                                                          | U1301                                                                                            |

| 39070085   | Battery Management IC,4.1~16V,DC-DC Charger,Smart Pow<br>er Control,QFN,SMT,Terminal Dedicated                                           | U1900                                                                                            |

| 40060318   | NAND Flash, 16GB EMMC V4.4, 52MHz, 1024KB, 3.3V, FBGA169(Pb-Free), Terminal Dedicated                                                    | U1100                                                                                            |

| 40060344   | MCP, 2Gb(256M*8bit) NAND,23MHz,128KB,1.8V,VFBGA1<br>30(Pb-free),1G (32M*32bit) Mobile LPDDR SDRAM,Balong<br>Dedicated,Terminal Dedicated | U2601                                                                                            |

| 51623731   | DKBA80359313,S7-931U-POWER-FRAME                                                                                                         | J2502                                                                                            |

| 51623727   | DKBA80359309,RGB-FRAME,S7-931U                                                                                                           | J2503                                                                                            |

| BOM Number | Description                                                                                                                                    | Remarks         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 51623736   | DKBA80359318,S7-931U-WIFI-FRAME                                                                                                                | J2504           |

| 51623733   | DKBA80359315,S7-931U-CODEC-FRAME                                                                                                               | J2505           |

| 51623729   | DKBA80359311,S7-931U-FLASH-FRAME                                                                                                               | J2506           |

| 51623725   | DKBA80359307,BB-FRAME,S7-931U                                                                                                                  | J2507           |

| 12070038   | Temperature Compensated Oscillator,26MHz,+/-1.5ppm(max),<br>+1.8V,+/-0.5ppm(max),-40degC,85degC,Terminal Dedicated                             | TCXO2300        |

| 39200455   | Terminal Baseband process IC,Digital Base Band Processor-<br>1.2GHz-RK2918,1.2/1.8/2.6/2.5/3.3V,TFBGA512,Terminal De<br>dicated                | U4              |

| 39110682   | LDO,2.5V,2%(Max),0.3A,SOT23-5,Terminal dedicated                                                                                               | U1000           |

| 39110548   | LDO,3.3V,2%,0.15A,SC70-5,Terminal Dedicated                                                                                                    | U1001,<br>U1300 |

| 39110490   | Voltage Regulator,1.2V LDO Regulator,2%,0.15A,SOT-23-5<br>A,Terminal Dedicated,BT                                                              | U1002           |

| 39110471   | Voltage Regulator,2.85,3%,0.15A,SOT-23-5,Terminal Dedicat ed (from39110307)                                                                    | U1200           |

| 43140104   | Interface Controller, RGB to LVDS, 1.8/3.3V, Terminal Dedic ated                                                                               | U1301           |

| 40060386   | NAND Flash, 8GB(x8bit) MLC,40MHz,8192KB,3.3V,TSOP4<br>8(Pb-Free),S7-Lite Dedicate,Terminal Dedicated                                           | U1302           |

| 36020411   | CMOS,8BIT Level Shifter With Automatic Direction Sensin<br>g,SDIO Bus Application,WCSP20,7ns,50mA,CMOS,CMOS,2<br>5nS,Terminal Dedicated,117C/W | U1500           |

| 36020401   | CMOS,2BIT-1.8V/3.3V Level Shifter,GFN8(Pb-free),1.5ns,14<br>mA,CMOS,Open drain,Terminal Dedicated                                              | U1501,<br>U6002 |

| 43110077   | AUDIO Chip,QFN,CODEC,Support I2S,PCM Interface,ACE,<br>Terminal Dedicated                                                                      | U1600           |

| 39080127   | Operation Amplifier, Audio Power Amplifier, 2.5V~5.5V, Diffe<br>rencial, Micro SMD 9pin(BGA Pb-Free), Terminal Dedicated                       | U1700           |

| 39110709   | Power Driver,2A Boost DCDC,QFN10,Terminal Dedicated                                                                                            | U1702           |

| 32050033   | Vibrator,Cylindrical,3.0V,0.11A,11000rpm,10.5mm*4.5mm*4.<br>85mm,SMT, SANYO, 28.50hm,Terminal Dedicated                                        | U1703           |

| 39070073   | -0.3~2.75V,Battery Gauge,SON,Terminal Dedicated                                                                                                | U1800           |

| BOM Number | Description                                                                                                             | Remarks                             |

|------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 39070117   | Battery Management IC, 4.2V,18V,Charger with separate Po<br>wer Path Control,WCSP,SMT,Terminal Dedicated                | U1801                               |

| 38140064   | Semiconductor Sensor, Accelerometer, LGA, 3axis, Terminal Dedicated                                                     | U1900                               |

| 39070145   | Voltage Monitor,2.7V, Delay Reset Chip,0.9V-6V,SOT23-3,T erminal Dedicated                                              | U2000                               |

| 47140049   | RF Switch,0.5~3.0 GHz,SP3T,0.45dB,1.22,20dB,TSON,200~2<br>60V(HBM),Terminal Dedicated                                   | U2100                               |

| 39210036   | Terminal Baseband Peripheral IC,GPS Receiver,support GLO NESS,2.3~5.5V-WLBGA42(Pb-free),Terminal Dedicated              | U2300                               |

| 47090053   | RF LNA,1575MHz,14dB min.,1.6dB max.,SOT886,Terminal Dedicated                                                           | U2301                               |

| 36020366   | CMOS,4BIT Level Shifter With Automatic Direction Sensin<br>g,WLCSP(Pb-free),7.4ns,50mA,CMOS,CMOS,Terminal Dedic<br>ated | U2400                               |

| 51078365   | MU509-b,HSDPA/WCDMA 2100/900 EDGE/GPRS/GSM Fo<br>ur Band,China Hubei Open Market,Module,Media Pad                       | U2401                               |

| 40020189   | DDR3 DRAM,2Gb DDR3,1600MHz,8bit,1.5V,FBGA78,Term inal Dedicated                                                         | U5000,<br>U5001,<br>U5002,<br>U5003 |

| 39130135   | RTC,Real Time Clock,TSSOP8, Terminal Dedicated                                                                          | U6000                               |

| 38020033   | Analog Switch, Single Channel Bidirectional, 1.65-5.5V, 7~500<br>hm, 250MHz, SC-70, SC-88                               | U6001                               |

| 36020336   | LVCMOS-Unbuffer Single Inverter<br>Gate-SC-70-9ns-4mA-CMOS-CMOS                                                         | U6003                               |

| 39110566   | Switching Regulators,1~4V,1.5A,SMT,Terminal Dedicated                                                                   | U9000,<br>U9001,<br>U9002,<br>U9003 |

| 36020382   | CMOS-Power on reset-MLP-8 2 x 2 x 0.8mm,0.5mm<br>Pitch-300ns-0.5mA-COMS-COMS-3ns                                        | U9004                               |

| 12020216   | Crystal,37.4MHz,10pF/8.3pF/9pF,+/-10ppm,80ohm,2016,Term inal Dedicated                                                  | X2100                               |

| 12020125   | Crystal,0.032768MHz,12.5pF+/-30ppm,60/80kohm,3.2*1.5 S<br>MD,Terminal Dedicate,ELOM,TS16949                             | X6000                               |

| BOM Number | Description                                                        | Remarks |

|------------|--------------------------------------------------------------------|---------|

| 12020171   | Crystal Oscillator,27MHz,12pF,20 ppm,50ohm,3225                    | X6001   |

| 12020151   | Crystal,24.000MHz,12pf,+/-v30ppm,50ohm,HCX-3SB,Termin al Dedicated | X6002   |

# **4** Principles and Failure Analysis

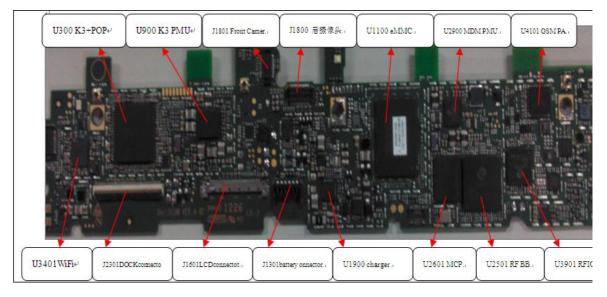

# 4.1 Working Principles of the MediaPad 10 FHD

The MediaPad 10 FHD consists of a PCBA, a small I/O board, and a small headset board.

The PCBA is designed based on a combination of the AP (Hisilicon K3V200) and the Balong V7 modem. The BCM4330 solution developed by Broadcom is used for the Wi-Fi and Bluetooth modules. The GPS implements the functions of both the AGPS and the GLONESS. Currently, the GPS can already provide basic functions but temporarily there is no specific test specification for it. The BCM47511 solution launched by Broadcom is applied to the GPS. The MediaPad 10 FHD uses the K3V200 system, to which the modern Balong V7, BCM4330, BCM47511, and other subsystems are attached. There is an independent storage module for both the AP and the modem. The 16 Gbit LP DDR RAM provides a memory unit for the AP program. System and application programs are stored in a large-capacity eMMC. The modem module has an independent storage unit and memory to store related data and guarantee its normal operations. An independent PMU is designed for both the AP and the modem to separately supply power to them. That is, the power management IC Hi6421 supplies power to the AP, and the power management IC Hi6451 supplies power to the modem. When a power-on event is triggered, the power management IC Hi6421 is powered on first. After the AP system is started, the power-on process starts on the Hi6451 so that the modem system is started.

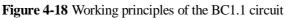

Figure 4-1 shows the functional blocks of the PCBA.

#### Figure 4-1 Functional blocks of the PCBA

Figure 4-2 shows the layout of components on the PCBA.

Figure 4-2 Layout of components on the PCBA

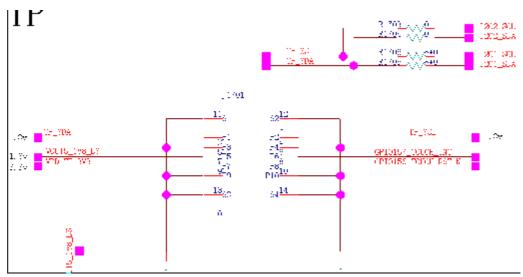

Figure 4-3 shows the physical architecture of the PCBA, where the interface connections of various modules are indicated. The application processor Hi3620 has three MPI interfaces. The CSI interface is connected to the LCD module. The CSI0 interface is connected to the rear camera. The rest MIPI interface is a multiplexing of DSI and CSI to provide digital connections for the front camera.

A 32-bit parallel bus is designed to transmit data between the LP DDR RAM and the CPU system, and the eMMC uses an 8-bit SDIO parallel port for data transmission. The PMU and codec are integrated in the Hi6421. The Hi3620 controls power settings through the SPI interface. The Wi-Fi data link is established on a 4-bit SDIO interface. The GPS and Bluetooth modules involve a small data volume, using the high-rate serial port UART as the data transmission channel.

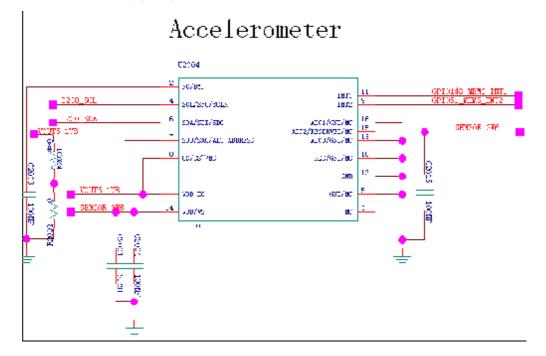

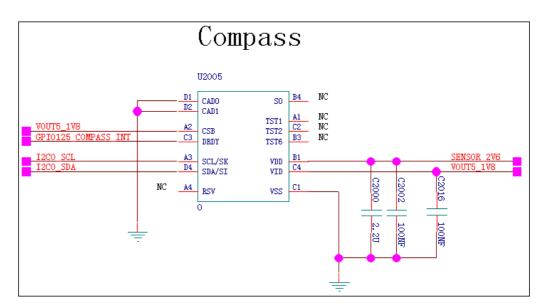

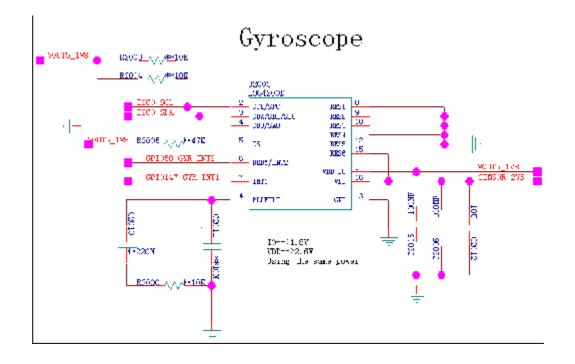

Brand-new HSIC interfaces are used to provide high-rate data channels before the AP and the modem. The interface rate is up to 480 MHz. High-rate serial ports (HSUART) serve as auxiliary control channels. The memory unit consists of a 32-bit parallel bus, and the storage unit uses 16-bit parallel ports. External sensors, such as the acceleration sensor, compass, and gyroscope sensor, are connected to the system through I2C interfaces.

#### Figure 4-3 Physical architecture of the PCBA

## 4.2 Power-On and Power Tree

#### 4.2.1 Hardware Startup Process

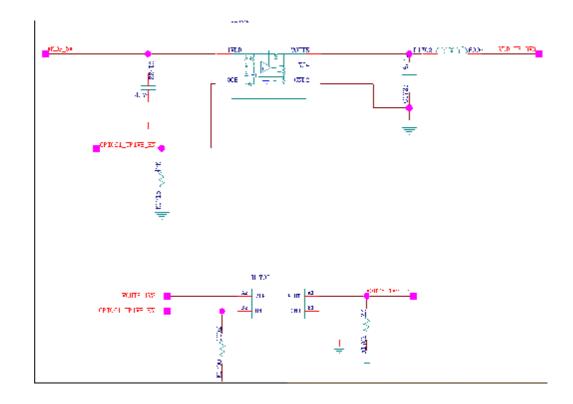

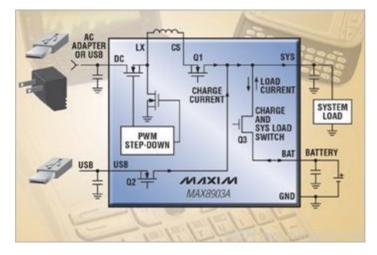

Figure 4-4 shows a power-on and power-off sequencing diagram.

| Time that the first<br>power starts to be<br>powered on<br>RST1_NRST2_N | PUT PUT                                                                                                                          | theilthe Time that the<br>Insert is crystal oscillator is<br>savefiel stable. | Time that the global next is descented. | Time that the All'<br>abstra to be<br>powered oft | POR<br>reset time power of a<br>complete.                |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------|----------------------------------------------------------|

|                                                                         | The hardware reset delays 60 ms.                                                                                                 |                                                                               |                                         |                                                   |                                                          |

| POR_n AP is internal power-on meet 20 me deboarce                       | POR, n hysteresis time : 2 me to 8 m<br>(The POR need can be destanted<br>after the I/O power is statile.)                       |                                                                               |                                         |                                                   |                                                          |

| ADDK Powerup                                                            |                                                                                                                                  |                                                                               |                                         |                                                   |                                                          |

| PWITION Power up<br>12 ms<br>deburger                                   |                                                                                                                                  |                                                                               |                                         |                                                   |                                                          |

| PWRHOLD(GPO)                                                            |                                                                                                                                  |                                                                               |                                         |                                                   |                                                          |

| nuos                                                                    | BUCKS that the FMU provides to LDO<br>and LDO3 must be powered on find. Th<br>AP of BUCK is invisible.                           | 2                                                                             |                                         |                                                   |                                                          |

| LDO2 120 µs                                                             |                                                                                                                                  |                                                                               |                                         |                                                   |                                                          |

| BUCK3                                                                   |                                                                                                                                  |                                                                               |                                         |                                                   |                                                          |

| BUCKD/1                                                                 | bowe.<br>bowe                                                                                                                    |                                                                               |                                         |                                                   |                                                          |

| 90 (10)                                                                 |                                                                                                                                  |                                                                               |                                         |                                                   | T I                                                      |

|                                                                         | U power                                                                                                                          |                                                                               |                                         |                                                   |                                                          |

| LDOSLDOSLDO7 120 H                                                      | LDOS 1.5 V power of the AP LPDDR2. When o<br>LDOS 2.5 V digital VO power of the AP<br>LDO7 2.5 V power of the AP high-speed SD K |                                                                               | ver must supply power before the 1.2 V  | power.                                            | The time internal that each powe<br>powered off is 60 pa |

| BUCK4LDO3LDO4LDO8                                                       | LD03 and BUCK4.1.2 V I/O powers (LPDDR2)<br>LD04 provides a 2.5 V analog power.<br>LD08 provides a 3.3 V analog power for the UI |                                                                               | two 1.2 V powers supply power togeth    | e. 📄                                              | $\backslash$                                             |

| 1000                                                                    | 2.85 V power of the MLC<br>NAND fleich and eMMC                                                                                  |                                                                               |                                         |                                                   | <u> </u>                                                 |

| [<br>말[0]                                                               | Crystal cecilitor working power<br>of the PMU                                                                                    |                                                                               |                                         |                                                   | <u></u>                                                  |

| CUC 25M                                                                 |                                                                                                                                  |                                                                               |                                         | ותחחחו                                            |                                                          |

|                                                                         | Time that the crystal oscillator i<br>(the time is determined by the analog                                                      |                                                                               |                                         |                                                   |                                                          |

| сик,зак                                                                 |                                                                                                                                  |                                                                               |                                         |                                                   | וחחו                                                     |

#### Figure 4-4 Power-on and power-off sequencing

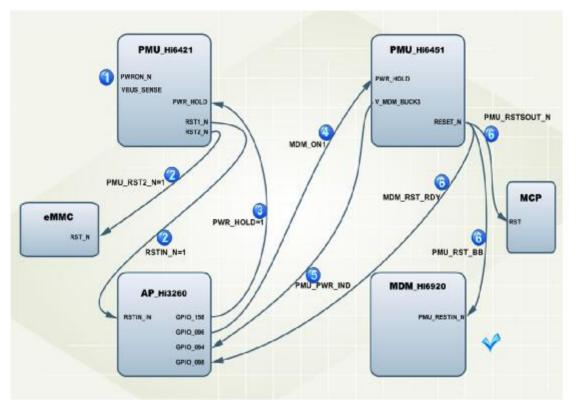

Figure 4-5 shows the power-on procedure.

#### Figure 4-5 Power-on procedure

The power-on process consists of the following steps:

- 1. A power-on event is triggered.

- 2. The AP\_PMU sends two reset signals, one to the AP and the other to the eMMC.

- 3. The AP returns a HOLD signal to the AP\_PMU after being reset.

- 4. The AP sends a power-on signal to the MDM\_PMU to trigger the power-on of the MDM\_PMU.

- 5. The MDM\_PMU BUCK3 returns a PWR\_OK signal to the AP after being powered on.

- 6. The MDM\_PMU sends a reset signal to reset the MCP and MDM, and sends a notification to the AP, indicating that the MDM is ready following the reset.

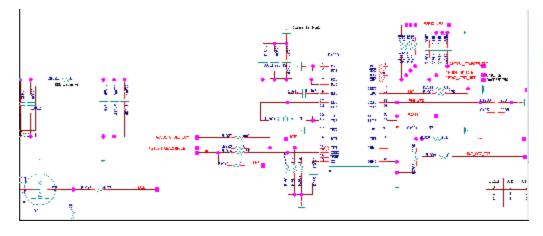

#### 4.2.2 Power Tree

# 4.3 Circuit Analysis and Troubleshooting for Functional Units

### 4.3.1 Working Principles of the AP Subsystem

Figure 4-6 shows the AP framework.

#### Figure 4-6 AP framework

The K3V200 system uses the Hi3620 chip as its core to provide the following logical interfaces:

#### NAND/eMMC Interface